Lighting up your life Pg 26

Megabit DRAMs and the PC boom Pg 30

SEP

Issue 19/2006 www.edn.com

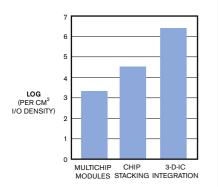

Analog Domain looks at how things are stacking up Pg 32

Perking up voltageregulator droop Pg 34

Design Ideas Pg 73

100.0

View

10010

VOICE OF THE ENGINEER

### Eight years later, details still matter Page 46

CLICK HERE TO RENEW SDR GOES TO WAR Page 39

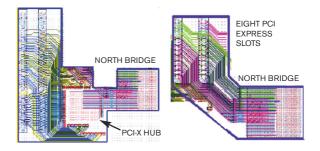

> ABRACADABRA: MAKING SYSTEM INTERCONNECT DISAPPEAR WITH FPGAs Page 59

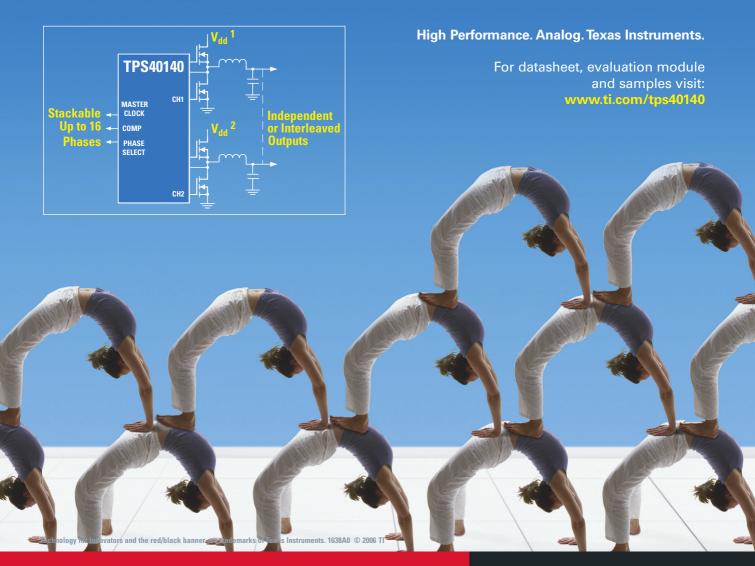

# Stackable. Scalable. Flexible. DC/DC Controller Boosts Efficiency

The TPS40140 turns power supplies in data center and telecommunication equipment into fully scalable, stackable power systems with greater load-handling capability and maximum efficiency. This unique PWM buck controller offers the simplicity of a stand-alone dual or two-phase controller with the ability to "stack" multiple devices together, creating a high-density power supply. Generating from 10 A to 320 A of output current, true interleaved operation enables maximum efficiency up to 16 phases.

### Technology for Innovators"

Quality Components Just a Click Away!

1.800.344.4539 • www.digikey.com \* New Product Added Daily!

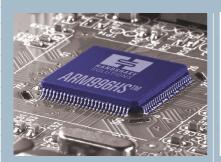

### **Back a winner!**

Atmel's ARM<sup>®</sup>-based 32-bit microcontrollers are winners. They have already picked up four prestigious awards from readers of industry leading magazines\*. Why? Because they give you exactly what you want. On-chip Flash memory. USB & Ethernet connectivity. DMA to eliminate internal bottlenecks. Supervisory functions. All this at the lowest

possible power consumption and unit price, plus code compatibility across the entire product family. So, make your application a winner by backing a winner: Atmel's AT91SAM Smart ARM-based microcontrollers.

\* EEProductCenter Ultimate Product (Processor & Memory) for Q4 2004 and again for Q4 2005, Embedded Control Europe Gold Award (Micros & DSP) for H2 2005, 2006 EETimes ACE Award Ultimate Product of the Year.

Learn more about our AT91 products by visiting our web site, at www.atmel.com/ad/at91 and register to qualify for a free AT91SAM7 development kit. You will also receive an AT91 DVD with extensive product documentation, training material, application notes and code samples.

Check out Atmel's AT91 solutions at www.atmel.com/products/at91

© Atmel Corporation 2006. All rights reserved. Atmel<sup>®</sup>, logo, combinations thereof, Everywhere You Are<sup>®</sup> and others are registered trademarks of Atmel Corporation or its subsidiaries. ARM<sup>®</sup> is the registered trademark of ARM Ltd. Other terms and product names may be trademarks of others.

Everywhere You Are®

### ▼

Feedback on the prototype heater assembly:

Ming says it's not accurate enough. Sarah doesn't like the controller. Ted says it won't fit.

What do they expect? You can't pull miracles out of a parts book.

## Don't compromise. Customize.

Having trouble turning a prototype into a product? Just call Minco. Our custom integrated assemblies give you cost-efficient design options and robust performance you can't get off the shelf. Talk with a Minco engineer at **763.571.3121**. Or visit **www.minco.com/edn**

INSTRUMENTS

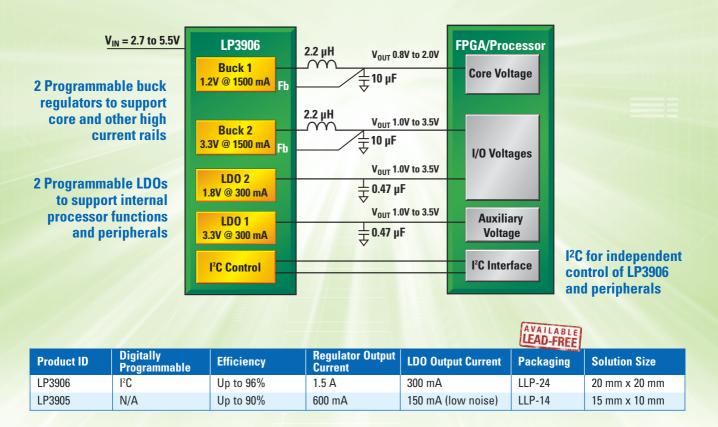

# Easy-to-Use Power Management Units for Digital Subsystems

### 96% Efficient LP3906 Provides Flexibility with Digital Programmability

Ideal for powering application processors, FPGAs, and DSPs where size and efficiency are important

Expert tips, tricks, and techniques for powerful designs. Sign up today at **power.national.com/designer**

For FREE samples, datasheets, online design tools, and more, visit us today at: power.national.com

Or call 1-800-272-9959

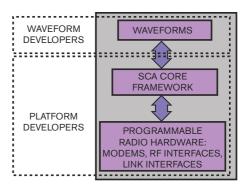

### Abracadabra: making system interconnect disappear with FPGAs

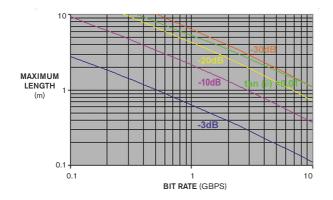

59 Advanced signalconditioning techniques can solve interconnect problems. by Andy Turudic, Altera Corp

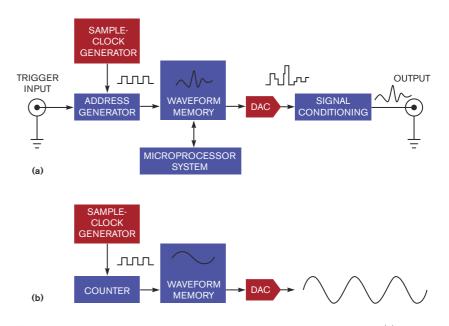

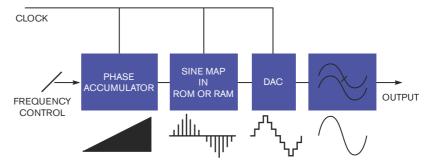

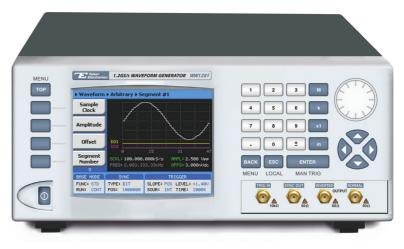

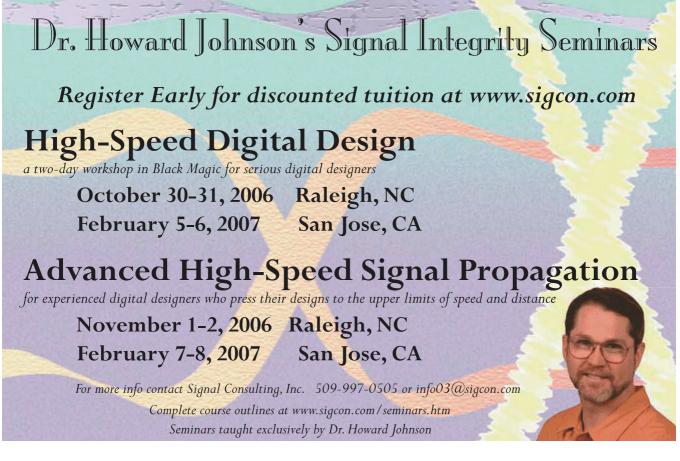

### Making waves: Eight years later, details still matter

46 Understanding waveform-generator operation and specifications before you buy is as important today as it was eight years ago. by Dan Strassberg, Contributing Technical Editor

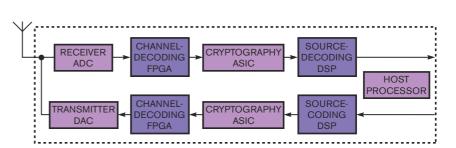

SDR goes to war

39 The JTRS is working to bring interchangeable SDR to the military. But will it be good enough for commercial applications? *by Nicholas Cravotta, Contributing Technical Editor*

# DESIGNIDEAS

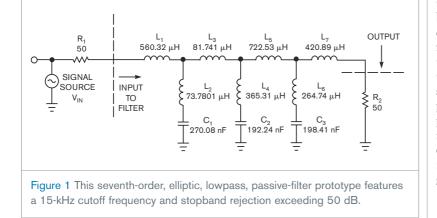

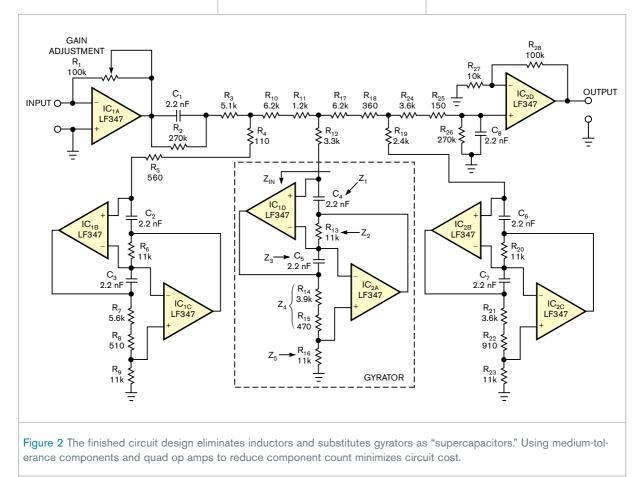

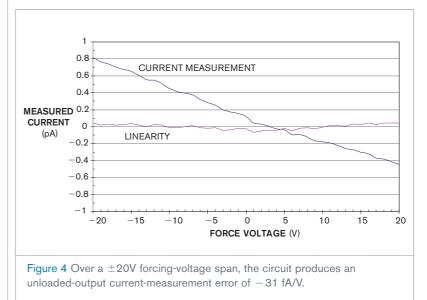

- 73 "Brick-wall" lowpass audio filter needs no tuning

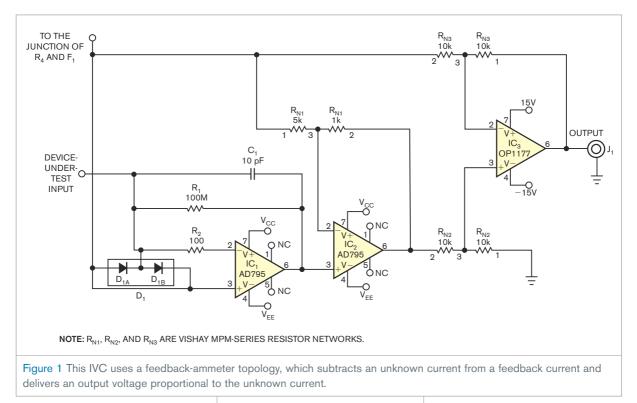

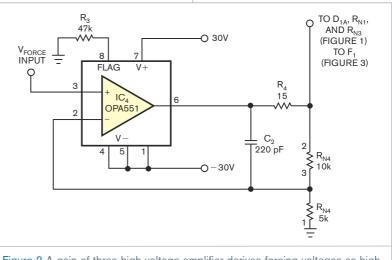

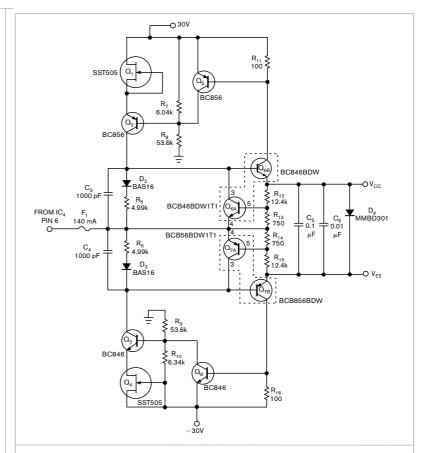

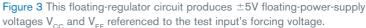

- 74 Fast-settling picoammeter circuit handles wide voltage range

- Send your Design Ideas to edndesignideas@reedbusiness.com.

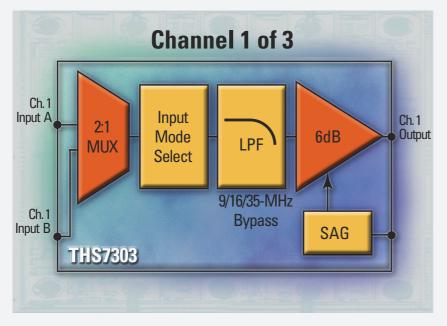

# 3-Ch. Low-Power Video Amp with I<sup>2</sup>C Control

The **THS73x3** family of high-performance video amplifiers from Texas Instruments provides the designer with unprecedented flexibility and control in configuring video systems without the need for hardware upgrades or modifications. Operating at 20x less power than competing amplifiers, these products are ideally suited for digital video systems like those incorporating TI's DaVinci<sup>™</sup> and DLP<sup>®</sup> technologies.

| Device  | # of | Filter -3 dB<br>Freq<br>(MHz) (typ) | Filter | Bypass<br>Bandwidth<br>(MHz) (typ) | Gain<br>(dB)     | Input<br>Coupling                   | Output<br>Coupling | SAG<br>Output | Price<br>Starts<br>at 1K |

|---------|------|-------------------------------------|--------|------------------------------------|------------------|-------------------------------------|--------------------|---------------|--------------------------|

| THS7303 | 3    | 9, 16, 35                           | 5      | 190                                | 6                | AC-Bias,<br>AC-STC,<br>DC, DC+Shift | AC or DC           | Yes           | \$1.65                   |

| THS7313 | 3    | 8                                   | 5      | -                                  | 6                | AC-Bias,<br>AC-STC,<br>DC, DC+Shift | AC or DC           | Yes           | \$1.20                   |

| THS7353 | 3    | 9, 16, 35                           | 5      | 150                                | 0,<br>Adjustable | AC-Bias,<br>AC-STC,<br>DC, DC+Shift | AC or DC           | No            | \$1.65                   |

### Applications

- Set-top boxes

- Digital televisions

- Personal video/DVD recorders

- Portable USB devices

### ► Features

- 2.7V to 5V single-supply operation

- Low power consumption: 55mW at 3.3V

- 2:1 Input MUX allows multiple input sources

- I<sup>2</sup>C Control of all functions

- Integrated low-pass filters with 5th-order Butterworth characteristics

- Selectable input coupling modes

- Rail-to-rail outputs allow a variety of AC- or DC-coupled modes

- Individual channel disable with independent channel mute control

For Samples, Evaluation Modules and Technical Information

**TEXAS INSTRUMENTS**

### www.ti.com/ths7303 ° 800.477.8924, ext. 13277-

Technology for Innovators<sup>™</sup>

# contents 9.14.06

C-C Dilbert 22

- 21 Test set speeds next-generation wireless-device calibration

- 21 Dual computers boost system performance

- 22 Hall-effect hot-swap controller debuts

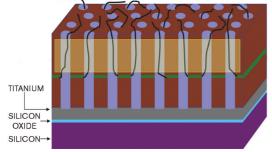

- 24 32-nm CMOS begins to take shape

- 26 **Research Update:** Process coaxes carbon nanotubes into service as vias; Magnetic material may put new spin on computing; Your name in lights, on your body; Nanoscale cavity amplifies LED output by seven times

- 28 Global Designer: Receivers target high-volume GPS and DVB-H applications; New US passports contain secure identification chips

## DEPARTMENTS & COLUMNS

- 14 EDN.comment: Kamen clobbers big-company management

- 30 Milestones That Mattered: Megabit DRAMs led PC boom, despite claims that they were "too capacious"

- 32 Analog Domain: Stacking up

- 34 **Signal Integrity:** Voltage-regulator droop

- 36 Tales from the Cube: Perceptions and realities

- 88 **Scope:** The ARM Developers' Conference, notebook PCs, and more

# PRODUCT ROUNDUP

- 82 Sensors and Transducers: 64-photodiode sensor assemblies, light-to-digital sensors, interface ICs, finger-tip sensors, and more

- 83 Test and Measurement: PCI-digitizer cards, debugging-tool upgrade, and more

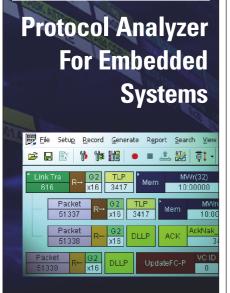

- 84 Embedded Systems: Software-radio transceivers, flat-panel touchscreen computers, VMEbus blades, miniature motherboards with audio/video capabilities, and more

EDN ® (ISSN#0012-7515), (GST#123397457, R.B.I. Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer, Stephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN ®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN ® copyright 2006 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year; Canada \$226 one year, (includes 7% GST, GST#123397457); Mexico, \$215 one year; air expedited, \$389 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Mail Agreement No. 40685520. Return undeliverable Canadian addresses to: Deutsche Post, 4960-2 Walker Road, Windsor ON N9A GJ3. E-mail: subsmail@reedbusiness.com. Please address all subscription mail to EDN ®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Televier Properties Inc, used under license. A Reed Business Information Publication-Yolume 51, Number 19 (Printed in USA).

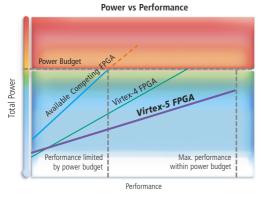

## **TRIPLE-D** Ultimate Power Optimization . . .

Note: Under worst-case operating conditions (85°C)

# Reduce power without compromising performance.

Virtex<sup>™</sup>-5 FPGAs give you unbeatable power savings with the highest performance. The unique combination of 65nm process, second-generation Triple-Oxide technology, ExpressFabric<sup>™</sup> architecture, and power-optimized hard IP extends the 1 to 5 Watt power advantage delivered by previous-generation Virtex FPGAs. Achieve higher reliability and a smaller form factor. Save cost on power supplies, heat sinks, and fans. All this, plus the industry's highest performance. No other FPGA vendor comes close.

### Meet performance targets within your power budget

Our Triple-Oxide technology optimizes multiple oxide thicknesses to control leakage and keep static power on par with 90nm Virtex FPGAs while maximizing performance. New 65nm ExpressFabric architecture with real 6-input LUTs and diagonally symmetric routing reduces dynamic power by at least 35%. With power-optimized hard IP and automated, block-based power control, you can save even more. With Virtex-5 FPGAs, you can meet your most aggressive performance *and* power targets. No compromises.

Visit **www.xilinx.com/virtex5/power,** view the Virtex-5 power webcast, download the XPower Estimator tool, and read the power analysis white paper.

www.xilinx.com/virtex5/power

The Ultimate System Integration Platform

Virtex-5 LX is the first of four platforms optimized f Logic, DSP, processing, and serial connectivity.

Expert tips, tricks, and techniques for analog designs

### Vol. IV, Issue 9

## **Optimizing Portable Applications with D/A Converters**

By Chuck Sins, Applications Engineer

esigners of portable electronic devices have several methods available for using general-purpose Digital-to-Analog Converters (DACs) to digitally adjust voltages and enhance the performance of portable devices.

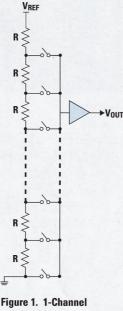

DACs are most easily understood by examining a simplified DAC block diagram. As shown in Figure 1, the architecture of a one-channel DAC consists of a resistor array (each of equal value R) followed by a rail-to-rail voltage output amplifier. The voltage applied to the reference pin is the voltage at the top of the resistor array and a switch is connected between each pair of resistors and one to ground. The voltage is tapped off by closing one of the switches and connecting this point on the array to the amplifier. The resistor array and output amplifier consume very little power and emit no switching noise since the DAC is static once the

**DAC Architecture**

specified resistor tap has been connected to the amplifier. In addition, multi-channel DACs packaged in a 3 mm by 3 mm Leadless Leadframe Package (LLP®) occupy very little board space in portable applications. An alternative to using a DAC is a resistive trim potentiometer. However, these devices are large in size, suffer from mechanical wear, and are not digitally controllable.

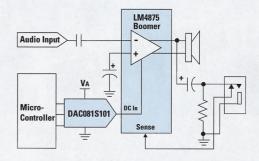

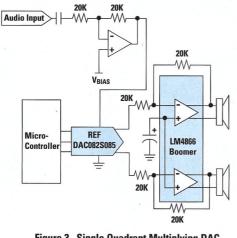

Over the last couple of years, the audio capability and LCD display quality of cell phones have improved tremendously, while the size and cost of the phones have gone down. Most phones today have a headphone jack, an earpiece, and a built in loudspeaker. All three of these audio outputs require some type of volume control. One way a DAC can provide volume control is when it is used in conjunction with an audio amplifier that has a built-in DC volume control. A micro-controller that receives input from soft keys on the display or push buttons on the case causes the DAC's output voltage to step up or down (Figure 2). Another way to control volume is to use a DAC as a single quadrant multiplier. This configuration consists of an amplifier gain stage that feeds the amplified audio input into the reference pin of the DAC (Figure 3). The Serial Peripheral Interface (SPI) of the DAC is used to digitally attenuate the amplified audio input anywhere from full scale (0 dB) to zero volts. This is accomplished without adding any noticeable level of noise or distortion to the audio signal.

**DESIGN** *idea*

Figure 2. DC-Control of an Audio Amplifier

### **Featured Products**

### 1-Channel, Pin- and Function-Compatible DACs Across Resolutions

The 1-channel, pin- and function-compatible 8-, 10-, and 12-bit DACs each provide rail-to-rail output swing and input clock rates of 30 MHz over the entire supply range of 2.7V to 5.25V. The reference for each is derived from the power supply, resulting in the widest possible dynamic output range. A power-down feature reduces power consumption to less than 0.2  $\mu$ W, which is especially important for portable, battery-powered applications.

The on-chip output amplifier allows rail-to-rail output swing and the three-wire serial interface operates at clock rates up to 30 MHz over the specified supply voltage range and is compatible with standard SPI<sup>TM</sup>, QSPI, MICROWIRE, and DSP interfaces. The supply voltage serves as its voltage reference, providing the widest possible output dynamic range.

### **Features**

- Settling time: 10 µs

- Guaranteed monotonicity

- Low-power operation

- Rail-to-rail voltage output

- Power-on reset to zero volts output

- SYNC interrupt facility

- Wide power supply range: 2.7V to 5.5V

- Power down feature

Operating over the extended industrial temperature range of -40°C to +105°C, these DACs are ideal for battery-power instruments, digital gain and offset adjustment, programmable voltage and current sources, and programmable attenuators. The DAC121S101, DAC101S101, and DAC081S101 are available in TSOT-6 and MSOP-8 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/DC/DAC121S101.html www.national.com/pf/DC/DAC101S101.html www.national.com/pf/DC/DAC081S101.html

### Ultra Low-Power, 2-Channel, 8-/10-/12-Bit DACs

These general purpose DACs are full-featured and can operate from a single 2.7V to 5.5V supply and use 210  $\mu$ A at 3V and 320  $\mu$ A at 5V. The on-chip output amplifier allows rail-to-rail output swing and the three-wire serial interface operates at clock rates up to 40 MHz over the entire supply voltage range.

### **Features**

- INL (max)

- ±0.5 LSB (DAC082S085)

- ±2 LSB (DAC102S085)

- ±8 LSB (DAC122S085)

- DNL (max)

- +0.18 / -0.13 LSB (DAC082S085)

- +0.35 / -0.25 LSB (DAC102S085)

- +0.7 / -0.5 LSB (DAC122S085)

- Settling time (max)

- 4.5 μs (DAC082S085)

- 6 µs (DAC102S085)

- 8.5 µs (DAC122S085)

- Zero code error: +15 mV (max)

- Full-scale error: -0/75% FS (max)

- Wide power supply range: 2.7V to 5.5V

The 2-channel, 8-/10-/12-bit DACs are ideal for use in batterypowered instruments, digital gain and offset adjustments, programmable voltage and current sources, and programmable attenuators. The DAC082S085, DAC102S085, and DAC122S085 are available in MSOP-10 and LLP-10 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/DC/DAC082S085.html www.national.com/pf/DC/DAC102S085.html www.national.com/pf/DC/DAC122S085.html

### edge.national.com

# ANALOG edge"

### **Optimizing Portable Applications with DACs**

Figure 3. Single Quadrant Multiplying DAC

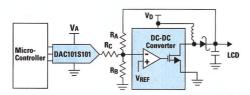

Many microprocessors can operate at a lower supply voltage to save power, and then operate at a higher supply voltage to increase their processing speed. Switching between these modes requires adjusting the output voltage of a DC-to-DC converter. Similar to microprocessors, LCD displays utilize DACs to control their contrast ratio. As the temperature of the display changes, the voltage applied to the display by the DC-to-DC converter must be adjusted to maintain the proper contrast ratio (Figure 4). Since neither of these applications require high speed adjustments, general purpose DACs are the ideal solution for digitally optimizing their performance.

Figure 4. DAC Controlling a DC-DC Converter

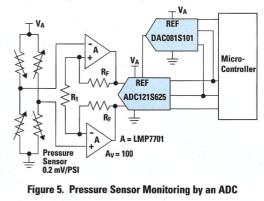

Portable devices that utilize sensors can also be enhanced with the use of general purpose DACs. Figure 5 illustrates a pressure sensor that is amplified and then monitored by a general purpose Analog-to-Digital Converter (ADC). Since the output of the amplifier stage has a large voltage range, the ADC requires a reference voltage equal or greater to the largest possible output voltage. While this is fine for measuring the sensor's output when it is at its maximum voltage, it is less than ideal for measuring the sensor's minimum output voltage. If a DAC was utilized as the reference voltage, the DAC could be digitally adjusted

based on the input to the ADC. This technique maximizes the accuracy of the ADC and allows the full range of codes to be utilized. The alternative solution is to use a more expensive ADC with a higher resolution in order to improve the system's accuracy. As a result, using a DAC in the circuit reduces the overall system cost while still providing the required accuracy.

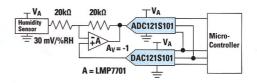

A similar application with a DAC enhancing system performance is a system that requires calibration for higher conversion accuracy. For example, a humidity sensor can be calibrated to a known ADC output code with the circuit in Figure 6. The sensor's output is applied to the negative input of the op-amp while a DAC output is connected to the positive terminal. The desired output code of the ADC can be achieved by digitally adjusting the DAC output voltage to the appropriate level. Higher resolution DACs deliver higher precision in the output reading.

Figure 6. Humidity Sensor Application

In all of these examples, general purpose DACs optimized a product's performance by digitally adjusting a voltage in the circuit without impacting the product's size, cost, or power consumption.

View over 50 design seminars by industry experts at www.national.com/onlineseminars

### edge.national.com

### **Featured Products**

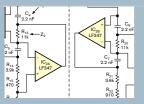

### **Precision, CMOS Input, RRIO Amps**

The LMP7701/02/04 are single, dual, and quad low offset voltage, rail-to-rail input and output precision amplifiers with CMOS input stage and wide supply voltage range. The rail-to-rail input stage significantly reduces the CMRR glitch commonly associated with rail-to-rail input amplifiers.

### **Features**

- Input offset voltage (max)

- ±200 µV (LMP7701)

- ±220 µV (LMP7702/04)

- Input bias current: ±200 fA

- Input voltage noise: 9 nV/√Hz

- 130 dB CMRR

- 130 dB open loop gain

- 2.5 MHz unity gain bandwidth

- Supply current

- 715 μA (LMP7701)

- 1.5 mA (LMP7702)

- 2.9 mA (LMP7704)

- Supply voltage range: 2.7V to 12V

The LMP7701/02/04 are ideal for high impedance sensor interfaces, battery-powered instrumentation, high gain amplifiers, DAC buffers, instrumentation amplifiers, and active filters. The LMP7701 is available in SOT23-5 packaging, the LMP7702 is available in MSOP-8 packaging, and the LMP7704 is available in TSSOP-14 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/LM/LMP7701.html www.national.com/pf/LM/LMP7702.html www.national.com/pf/LM/LMP7704.html

Ultra Low-Power, 4-Channel, 8-/10-/12-Bit DACs

These 4-channel, 8-/10-/12-bit DACs are full-featured and can operate from a single 2.7V to 5.5V supply and use 360  $\mu$ A at 3V and 480  $\mu$ A at 5V. The on-chip output amplifier allows rail-to-rail output swing and the three-wire serial interface operates at clock rates up to 40 MHz over the entire supply voltage range.

The reference serves all four channels and can vary in voltage between 1V and VA, providing the widest possible output dynamic range. A power-down feature reduces power consumption to less than a microWatt with three different termination options.

### Features

- INL (max)

- ±0.5 LSB (DAC084S085)

- ±2 LSB (DAC104S085)

- ±8 LSB (DAC124S085)

- DNL (max)

- +0.18 / -0.13 LSB (DAC084S085)

- +0.35 / -0.25 LSB (DAC104S085)

- +0.7 / -0.5 LSB (DAC124S085)

- Settling time (max)

- 3 µs (DAC084S085)

- 4.5 µs (DAC104S085)

- 6 µs (DAC124S085)

- Zero code error: +15 mV (max)

- Full-scale error: -0/75% FS (max)

- Wide power supply range: 2.7V to 5.5V

The 4-channel, 8-/10-/12-bit DACs are ideal for use in batterypowered instruments, digital gain and offset adjustments, programmable voltage and current sources, and programmable attenuators. These DACs are available in MSOP-10 and LLP-10 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/DC/DAC084S085.html www.national.com/pf/DC/DAC104S085.html www.national.com/pf/DC/DAC124S085.html

# EDN online contents

### Cool asynchronous designs emerge at Hot Chips

Patient supporters of asynchronous design may see vindication in presentations by Fulcrum Microsystems and Handshake Solutions.

→ www.edn.com/article/CA6364999

#### Architects adapt to the multicore era

Multiple threads gain favor over the quest for higher instruction-level parallelism within a thread.

→ www.edn.com/article/CA6366273

### Intel, AMD maneuver for position on next-gen architectures

Presentations at the Hot Chips conference highlight contrasting multicore approaches. -> www.edn.com/article/CA6364973

### Fast read-channel IP challenges integration methodology

Developing a 2.8-Gbps read channel is one thing. Making it compatible with a standard-cell design flow is another. → www.edn.com/article/CA6364595

**55-nm embedded-DRAM process debuts** The process may succeed in bringing embedded-DRAM architectures back to center stage in SOC applications.

Hot Chips panel sorts out couch ownership

Consumer-electronics and PC players argue over living-room domination. -> www.edn.com/article/CA6364986

READERS' CHOICE Recent articles getting high traffic on www.edn.com:

**Prying Eyes:** Wireless USB in a dongle → www.edn.com/article/CA6356069

Sifting the DFM players → www.edn.com/article/CA6360314

### Ultralow-cost, two-digit counter features few components

> www.edn.com/article/CA6360316

### Two-wire, four-by-four-key keyboard interface saves power

→ www.edn.com/article/CA6360317

### Gain-of-three amplifier requires no external resistors

> www.edn.com/article/CA6360318

#### Voltage-regulator model

→ www.edn.com/article/CA6360320

SiGe transistors hit 500 GHz → www.edn.com/article/CA6360327

Low-dropout regulator, SMPS cascade suppress ripple, maintain efficiency → www.edn.com/article/CA6356065

HD-DVD and Blu-Ray lack wow at debut → www.edn.com/article/CA6356068

Ceramic output capacitors enhance internally compensated switchers

→ www.edn.com/article/CA6351287

### **PRODUCT FEED**

Throughout *EDNs* 50-year existence, engineers have had a taste for *EDNs* product briefs: concise, no-nonsense writeups of new ICs and components. Now, we're proud to introduce *EDN* Product fEEd, a centralized online location for this critical part of our coverage.

We invite you to belly up to fEEd, where you'll find a daily dose of new products, as well as handy category filters that allow you to select the morsels that most interest you, be they analog or digital ICs, power components, sensors, passives, boards and systems, or software (to name just a few).

### EDN Product fEEd:

→ www.edn.com/productfeed

### RSS feed of the fEEd:

→ www.edn.com/ProductfEEdWebBlog. xml?nid=3066

### 2006 MICROPROCESSOR DIRECTORY

- Technical details on every processor family from more than 60 companies

- Filter based on your target application

- Exhaustive parametric tables

- More than 120 block diagrams

- Expanded analysis of each company and its offerings

- → www.edn.com/microdirectory

### BY MAURY WRIGHT, EDITOR IN CHIEF

## Kamen clobbers big-company management

s I promised in a previous column, I'll share some of Dean Kamen's thoughts on innovation, management, and leadership (**Reference 1**). Kamen is the founder of DEKA (Dean Kamen) Research and Development Corp (www.dekaresearch.com) and the inventor of the two-wheeled Segway human-transportation device. Kamen delivered an entertaining and enlightening keynote at last month's National Instruments Week conference in Austin, TX.

Early in his talk, Kamen discussed the typical project and inevitable dark times when success seems out of the question. He playfully suggested that when you plan a project that you "schedule a miracle." His message was about believing in and sticking with your idea. He quoted Winston Churchill, who said, "When you are going through hell, keep going."

Kamen presented a mythical project that a team plans over five years. After six months, the team is 10% into the project. "You'll never have an opportunity to know as much incremental new stuff as you did in the first six months because the denominator was zero," said Kamen. He contends that the 10% point is the best time to change the schedule or project. During those six months, the team may have figured out that the tasks are easier than expected or that bigger obstacles stand in the way. "At the end of six months, changing to four years or six years wouldn't be a big deal," he stated. He claimed that the impact is minor because the team is small; the burn rate is low; and the project hasn't incurred expenses for tooling, marketing, and other cost centers. He quipped, "I've never seen anybody do that. I've still got four years left to fix it; besides, it won't be my problem by then."

Kamen pointed out that a team more typically gets four and a half years into the project, when it's painfully clear that the project can't launch on time, and then changes the schedule. "It's the most expensive—the most painful time to do it," he said. The story drew laughs and applause from the crowd, who Kamen immediately challenged, asking, "You mean to tell me that any project that you've ever seen that finally was launched late, that you blew the whistle and made the changes as early as possible with the least risk cost? I don't think so—never works that way."

Although Kamen was advising better decision-making, he also suggested another way to prevent schedule slippage. He suggested: "Invent as a last resort." These days, especially with the Internet, someone else may have solved the individual problems that you face. Kamen also cautioned that you approach projects without preconceived bias. He related the story of a dialysis machine that DEKA redesigned. The earlier design used tubes that allowed fluid to flow "even when tied in a knot," and it also relied on compressing the tubes so that they worked as valves. Kamen related that the customer thought it wanted DEKA to solve its problem, but, in reality, the customer wanted him to fix its solution. DEKA ultimately delivered a different design. "It's not what we don't know that inhibits innovation; it's what we do know that just ain't so," he said.

Regarding management and leadership and their effect on innovation, Kamen stated, "Projects in big companies do require management. But innovation requires leadership, and I think they're not only not the same, they are diametrically opposed. ... Management is a process by which we make sure everything comes out the same. ... Good management would be to give a machine gun to an ax murderer; it would make the process more efficient. ... Management is doing things right. Leadership is doing the right things. Innovation, which is hard to do, is particularly hard to lead."

Kamen encourages innovation despite the inherent difficulty, pointing out that innovation creates entire industries. But he also asked: When should you innovate? The answer is now. He pointed out that, in his 30 years of experience, no one has ever asked him to work on the next-generation product while the current product is selling well and cash flow is great. Instead, he hears, "We're going to be toast in six months unless we do something. We've got to have a radically new idea. It's got to be out there, we don't have a lot of time, we don't have a lot of money, and you better get it right."

Finally, Kamen champions risk takers. "You don't define success as the lack of failure," he said. Unfortunately, management is about not trying to fail. He pointed out that optimists such as the Wright brothers were willing to fail without killing themselves—and the aviation industry was born.EDN

### REFERENCE

Wright, Maury, "Sportslike competition drives science and technology education," *EDN*, Sept 1, 2006, pg 12, www.edn.com/article/ CA6363908.

You can reach me at 1-858-748-6785 or mgwright@edn.com.

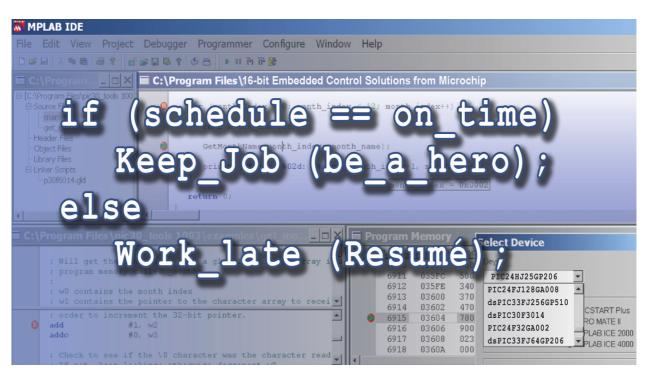

# Stay on Schedule

### **Envision: Add Features, More Performance, On Schedule**

Microchip's 16-bit Microcontroller (MCU) and Digital Signal Controller (DSC) solutions rapidly speed your application development to code freeze... and to production. Microchip offers the industry's only unified 16-bit MCU and DSC architecture with 32-bit performance and 8-bit simplicity. The PIC24F, PIC24H, dsPIC30F and dsPIC33F allow migration from low cost to high performance to DSP capability within the same low cost design environment. *Download our high quality development environment and test drive our C compiler for free today.*

### Spend less time optimizing code!

- Industry leading C code efficiency

- Selectable file level optimization for size or speed

- Architecture optimized for C

### Libraries shorten your design cycle and reduce risk

- TCP/IP, encryption, FAT16 file management, math and more

- Speech, audio, motor control and communication libraries

- Integrated peripheral driver library for (UART, SPI and more)

- DSP function library (FFT, IIR and more)

### Advanced software tools increase productivity

- Visual Device Initializer: auto-generated peripheral code

- DSP filters, motor control graphical user interface

- RTOS and scheduler

Get started with **FREE** MPLAB® IDE and MPLAB C30 C Compiler downloads at: **www.microchip.com/envision**

### Relative Code Size (Bytes)

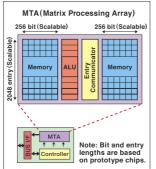

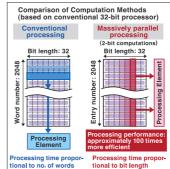

### Taking a new approach to matrix architecture by placing an ALU between memory components, Renesas Technology redefines graphics processing potential.

Multimedia data processing is the magic that makes consumer products such as digital movie cameras so exciting. It involves high-level arithmetic operations, including fast-Fourier transforms and convolution. Ordinarily, these essential calculations are handled by a specialized digital signal processor (DSP). But ever-increasing pixel counts and a proliferation of

multimedia data standards have pushed the humble DSP to its limits. It's time to advance to a new processing paradigm.

Leading that advance is Renesas Technology, with a massively parallel processor based on a matrix architecture that combines the processing performance of hardwired logic with DSP-like programmability. The unique design of this processor places an arithmetic logic unit (ALU) between memory components to handle arithmetic operations and enable simultaneous spatial processing of data aligned in parallel.

Massively parallel processing: Matrix architecture Revolutionary placement of an ALU between memory components eradicates data transfer bottlenecks. This innovative realignment makes a world of difference. It eliminates the need for loop operations and overcomes the bottleneck of data transfer between memory and ALU that can slow down conventional architectures. Greater performance, however, does not mean greater power con-

sumption. Our new matrix architecture processor achieves a clock

Massively parallel processing: Bit-serial, parallel-entry Achieving simultaneous spatial processing, as opposed to processing of data from top to bottom. frequency 30 times that of a conventional DSP, so it can achieve comparable performance operating at 1/30th capacity. Fast, flexible and surprisingly efficient, this processor is destined to fulfill the promise of the next-generation of multimedia technology and more.

With a revolutionary approach that challenges conventional wisdom, Renesas Technology has transcended the limits of DSP performance to speed progress of digital consumer products into the age of ubiquitous networking.

for Digital Consumer

RenesasTechnologyCorp. / www.renesas.com

COLUMNISTS Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn

PRODUCTION Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Brashears, Production Manager 1-781-734-8328; fax: 1-781-734-8086 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-781-734-8086 Pam Boord, Advertising Art 1-781-734-8313; fax: 1-781-290-3313

EDN EUROPE Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

> EDN ASIA Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

EDN CHINA William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

EDN JAPAN Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Kenji Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness.jp Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.io

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

DENNIS BROPHY Director of Business Development Mentor Graphics DANIS CARTER Principal Engineer, Tyco Healthcare CHARLES CLARK Technical Fellow, Pratt & Whitney Rocketdyne DMITRII LOUKIANOV System Architect, Intel RON MANCINI

Engineer

GABRIEL PATULEA Desian Engineer, Cisco

MIHIR RAVEL VP Technology, National Instruments

DAVE ROBERTSON

Product Line Director, Analog Devices

VP Network and System Architecture Division, Sonv

> TOM SZOLYGA Program Manager, Hewlett-Packard JIM WILLIAMS Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000; fax: 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# Logic Analysis to Digital ATE

### High-Speed Digital I/O

As part of the National Instruments mixed-signal suite, high-speed digital modules from NI offer the flexibility and features to address applications ranging from digital interfacing to advanced digital test.

| Features                 | Programmable<br>DIO          | LVDS<br>DIO | PCI Express<br>DIO    |

|--------------------------|------------------------------|-------------|-----------------------|

| Bus                      | PXI, PCI                     | PXI, PCI    | PCI Express           |

| Data Rate                | 100 Mb/s                     | 400 Mb/s    | 50 Mb/s               |

| Channels                 | 20                           | 16          | 32                    |

| Voltage                  | -2 to 5.5 V<br>(10 mV steps) | LVDS        | 2.5, 3.3,<br>or 5.0 V |

| Triggering               | 1                            | 1           | 1                     |

| Scripting                | 1                            | 1           | -                     |

| Hardware<br>Compare      | 1                            | -           | -                     |

| Applicatio               | ns                           |             |                       |

| Logic<br>Analysis        | 1                            | 1           | 1                     |

| Pattern<br>Generation    | 1                            | 1           | 1                     |

| BERT                     | 1                            | -           | -                     |

| Digital ATE              | 1                            | -           | -                     |

| Sustainable<br>Streaming | _                            | -           | 1                     |

To compare specifications and view application videos for the NI high-speed digital modules, visit **ni.com/highspeeddigital**.

© 2006 National Instruments Corporation. All rights reserved. National Instruments, NI, and ni.com are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 2006;6933:501-101-D

PUBLISHER, EDN WORLDWIDE

John Schirmer 1-408-345-4402; fax: 1-408-345-4400; jschirmer@reedbusiness.com

EDITOR IN CHIEF Maury Wright 1-858-748-6785; mgwright@edn.com

EXECUTIVE EDITOR Ron Wilson 1-408-345-4427; ronald.wilson@reedbusiness.com

MANAGING EDITOR Kasey Clark 1-781-734-8436; fax: 1-781-290-3436; kase@reedbusiness.com

EXECUTIVE EDITOR, ONLINE Matthew Miller 1-781-734-8446; fax: 1-781-290-3446;

mdmiller@reedbusiness.com SENIOR ART DIRECTOR Mike O'Legry

Mike O'Leary 1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

EMBEDDED SYSTEMS Warren Webb, Technical Editor; 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

> ANALOG Paul Rako, Technical Editor; 1-408-745-1994; paul.rako@reedbusiness.com

EDA, MEMORY, PROGRAMMABLE LOGIC Michael Santarini, Senior Editor; 1-408-345-4424; michael.santarini@reedbusiness.com

MICROPROCESSORS, DSPs, TOOLS Robert Cravotta, Technical Editor; 1-661-296-5096; fax: 1-781-734-8070; rcravotta@edn.com

MASS STORAGE, MULTIMEDIA, PCs AND PERIPHERALS Brian Dipert, Senior Technical Editor; 1-916-760-0159; fax: 1-781-734-8038; bdipert@edn.com

POWER SOURCES, ONLINE INITIATIVES Margery Conner, Technical Editor; 1-805-461-8242; fax: 1-805-461-9640; mconner@connerbase.com

DESIGN IDEAS EDITOR Brad Thompson edndesignideas@reedbusiness.com

SENIOR ASSOCIATE EDITOR Frances T Granville, 1-781-734-8439; fax: 1-781-290-3439;

f.granville@reedbusiness.com ASSOCIATE EDITOR Maura Hadro Butler, 1-908-347-9605; mbutler@reedbusiness.com

EDITORIAL/WEB PRODUCTION MANAGER Diane Malone, Manager

1-781-734-8445; fax: 1-781-290-3445 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-781-290-3442 Melissa Annand, Newsletter/Editorial Coordinator *Contact for contributed technical articles* 1-781-734-8443; fax: 1-781-290-3443 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-781-290-3325

CONTRIBUTING TECHNICAL EDITOR Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

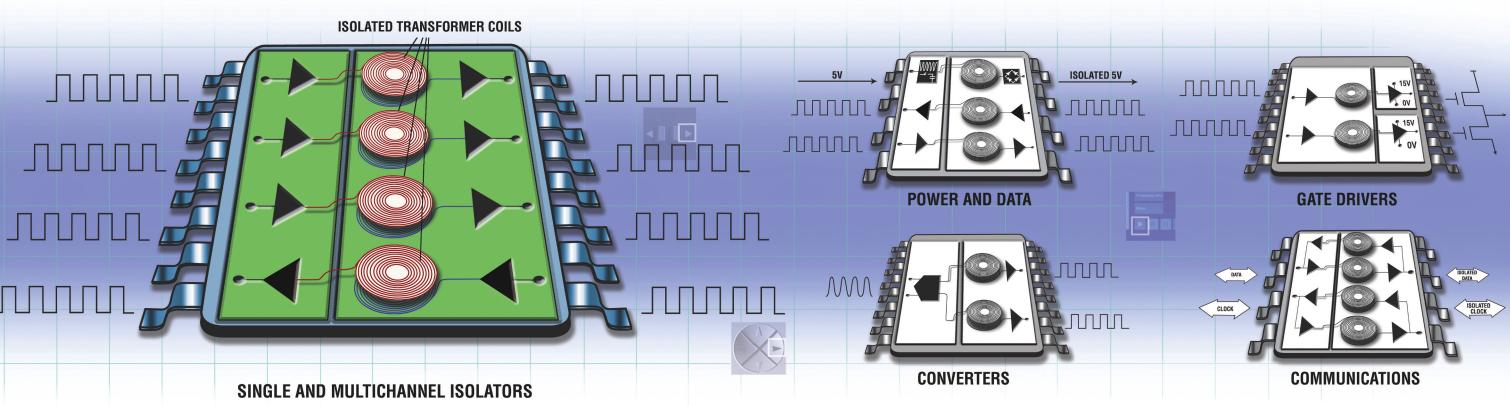

# Isolation and innovation in one package.

# With *i*Coupler, analog is everywhere.

### Isolating signals, power, and exceptional designs.

data isolation

iCoupler® digital isolators offer faster data rates, greater reliability, and up to 70% savings in board space and cost, vs. optocoupler solutions.

| Single and Multichannel Isolators |  |

|-----------------------------------|--|

|-----------------------------------|--|

Greater integration, performance, and reliability than optocouplers

#### ADuM1100/ADuM120x/ADuM130x/ ADuM140x/ADuM240x

- Single, dual, triple, and quad · Variety of input/output channel

- configurations

- 2.5 kV to 5 kV isolation

- Up to 100 Mbps data rate

- Starting at \$0.55/channel

All pricing in \$U.S. 1k quantities unless indicated. iCoupler products approved by UL, VDE, CSA, and TÜV.

#### isoPower™ Converters Industry's first digital Industry's leading isolator with integrated. converters with isolated power integrated isolation

ADuM524x family AD740x family • 50 mW isolated power • 16-bit, 10 MSPS • Variety of input/output • 3.75 kV isolation rating channel configurations Enables extreme

- Dual channel. 2.5 kV accuracy in current monitoring

- Starting at \$2.95 Starting at \$4.00

### **Gate Drivers** Compact isolation

solution for gate drive applications

#### ADuM1230 · High side isolated from

- low side

- 100 mA, high-side and low-side drive 2.5 kV isolation rating

- Starting at \$1.85

- 16 Mbps RS-485 transceiver

ADM2485

- Integrated transformer

- driver

**Communications**

Isolation tailored to

ADuM125x family

True bidirectional isolation for I2C® buses

• Starting at \$3.05

2.5 kV isolation rating

huses

specific communications

- 2.5 kV isolation rating

- Starting at \$5.50

### *i*Coupler technology: Over 75 million isolated channels

iCoupler technology represents the state of the art in digital isolation. Unlike common optocoupler isolation techniques, *i*Coupler combines chip scale transformer technology with analog and mixedsignal circuits for significant system level integration, cost savings, and functional advantages. These include:

- Standard isolators that offer faster data rates, greater reliability, and up to 70% savings in board space and cost

- with data converters, I<sup>2</sup>C, RS-485, and gate driver circuits

Eliminate the performance trade-offs of traditional isolation solutions. See why leading engineers have chosen *i*Coupler technology over optocouplers to isolate more than 75 million channels

For complete information on *i*Coupler technology, product portfolio, white papers, application notes, samples, and more, please visit our website

• New functionality: bidirectional data paths, combined signal and power isolation, isolation integrated

THINK Automotive Electronics.

THINK Zero Defects.

THINK Infineon.

YOU MAKE no compromises when it comes to quality. That's why we created Automotive Excellence, the industry's most rigorous zero-defect program.

AUTOMOTIVE EXCELLENCE redefines reliability and quality for automotive semiconductors. We don't settle for merely detecting defective parts. We develop holistic systems to prevent them, reducing costs and increasing customer satisfaction.

INFINEON HAS been dedicated to exceeding customer expectations in automotive electronics for **35** years. Today, our broad technology portfolio includes IC solutions for power train, safety management, and body and convenience. Our commitment to your success and our Automotive Excellence have earned us the **#2** position in the worldwide automotive semiconductor market.

WHEN YOU think of zero defects, think of the company dedicated to perfect quality with no compromises. Think Infineon.

www.infineon.com/us/auto

# EDITED BY FRAN GRANVILLE SCHOOL STREAM STRE

# Test set speeds next-generation wireless-device calibration

gilent Technologies has announced the availability of a next-generation wirelesscommunications test-set platform, which the company calls ideal for calibrating mobile phones in high-volume manufacturing. The test set provides industry-leading measurement speed and integrity as well as unique scalability—all targeting a decrease in the manufacturing cost of test.

The Agilent E6601A is an integrated test system in one box. It features a built-in, open-Windows XP PC, which allows the development, downloading, and execution of test programs directly in the system—eliminating the test-system PC and saving system space and cost. With a new measurement architecture that Agilent says targets high-speed measurements and accuracy, repeatability, and measurement integrity, the unit significantly lowers the cost of mobile-phone manufacturing test. In addition, the product provides reliability and low cost of ownership, the company claims.

One of the test set's key features is its speed—as much as 30% faster than other approaches. New calibration applications for GSM (Global System for Mobile communications), GPRS (General Packet Radio System), EGPRS (Enhanced GPRS), WCDMA (wideband code-division multiple access), and HSDPA (high-speed data-packet access) provide scalable, multiformat capabilities with only a software upgrade. For mobile-phone calibration, an optional fast device-tune measurement enables speeds as great as 10 times those of traditional methods. Connectivity is possible through 100BaseT LAN, IEEE 488, and six USB 2.0 ports.

The E6601A is the newest addition to Agilent's wireless-communications test-set product line, which includes the 8960 wireless-communications test set. As the company's flagship product, the 8960 continues to suit applications for wireless-device R&D, conformance test, manufacturing, service, and support. The E6601A costs \$27,100. A GSM/GPRS-calibration application costs \$6000, and a WCDMA-calibration application costs \$6000.-by Dan Strassberg

>Agilent Technologies, www.agilent.com.

The E6601A is a one-box integrated test system for nextgeneration mobilecommunications devices.

# Dual computers boost system performance

Many aerospace and military applications require redundant or parallel processors to achieve extended availability requirements and meet performance goals. So, why not include redundant hardware on a single board? General Micro Systems has accomplished that task with the new V469 Patriot VXS (VME-switched-serial) dual-processor, single-board computer. The company claims that the board provides the highest "horsepower density" per watt of any other current technology.

Unlike other dual-processor boards, Patriot uses two independent M-760 Pentium M processors that offer 100% redundancy, including power, cooling, and I/O. Each half operates at 2 GHz and has its own Fibre Channel connection with boot capability. The two halves communicate through a direct gigabit-Ethernet link. Support for the Patriot is available under Windows XP/2000, VxWorks-Tornado II, and Linux. Prices start at \$4700 (100).

-by Warren Webb General Micro Systems Inc, www. gms4sbc.com.

The V469 Patriot single-board computer packs two independent Pentium M processors plus peripherals onto a single VXS module.

# pulse

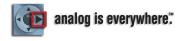

# Hall-effect hot-swap controller debuts

he new ACS760 series of ICs from Allegro Microsystems incorporates Hall-effect sensing to control inrush and protect the power buses in blade servers and other applications. This IC provides a major advantage over other approaches, which use a dropping resistor to yield a current measurement. These resistors are expensive, take up board space, and generate heat. Using a copper-board trace as the resistor is futile because the large TCR (temperature coefficient of resistance) of copper and the variation in board production make this method inaccurate and unreliable. In addition, engineers must design copper traces leading to the resistors to remove the resistor's heat. This approach takes up even more board space and creates a hot area that customers may perceive as a design shortcoming.

When you use these resistors in blade servers and other highdensity systems, all the heat from the sensing resistors can increase the budget for cooling fans and other peripherals. Heat also shortens semiconductor lifetimes in direct proportion to the heat at which they operate.

In addition, any dropping-resistor scheme must galvanically

### **FROM THE VAULT**

DSP ICs have reached the same point in their evolution that the  $\mu$ P had attained in the early 1970s, when the 8008 had demonstrated the promise of 8-bit general-purpose  $\mu$ Ps but the 8080 had yet to appear. The recent appearance of a DSP chip from Texas Instruments could mark the start of general-purpose use of DSP devices.

Robert Cushman, Special Features Editor, EDN, July 16, 1982, pg 44

connect to the bus, unless you design in complex and expensive isolation circuits. Optoelectronics all age significantly over their lifetime, making a stable, accurate, long-term isolation scheme a challenge to design. Allegro's ICs sense the magnetic field that the current flowing

In contrast to a traditional approach using dropping resistors (left), the ACS760 IC (right) uses Halleffect-sensing resistors to sense the current and control the bus power in hot-swap applications.

in the conductor creates and isolate the chip's power and output from the high-current bus. This approach can allow isolation to the bus if a user designs in the simpler isolation scheme for the bus NFET.

The ACS760ELF-20B can provide 240 VA of protection and inserts only 1.5 m $\Omega$  of resistance into the bus. In addition to controlling the gate of the N-channel high-side bus FET, it provides an analog-voltage output proportional to the signal. It also contains an overcurrent comparator that you can use to provide a digital trip point. An internal charge pump provides above-the-rail voltage to control an N-channel high-side FET. The IC operates at 10.8 to 13.2V. The analog-signal bandwidth is 50 MHz, and the circuit, including 12 pins for the dc bus, fits into a thin, 24-pin QSOP.

The first part in a future family, the ACS760 targets lowvoltage bus control, so it does not take advantage of the isolation that Hall sensing provides. Instead, it differentially senses the voltage at the load, so that it can account for the power calculations to provide thorough bus control. Allegro expects the ACS760ELF-20B to sell for \$2.48 (10,000).

-by Paul Rako **Allegro Microsystems**, www.allegromicro.com.

# Compact, Reliable, Embedded PCs

These go-anywhere SBCs operate where others can't. Rugged, reliable, and built for harsh environments, you will find PC-compatible architecture that will support Windows<sup>®</sup>, Linux, and x86-based software development tools.

- ▶ Platforms

- PC/104 3.6 x 3.8 inches

- EPIC 4.5 x 6.5 inches

- EBX 5.75 x 8.00 inches

- Software Support

- Windows® XPe

- Linux 2.6

- Windows® CE

- x86-compatible RTOS

- Quick start development kits

- Input/Output

- A/D and D/A

- Digital

- Serial

- GPS

- USB 2.0

- Communication Expansion

- GSM/CDMA Cellular

- 802.11 a/b/g Wireless

- 10/100/1000 Mbps Ethernet

- ▶ Long-life product availability

- ▶ -40°C to +85°C operation

Our SBCs are the right choice for industrial, transportation, pipeline, instrumentation, and MIL/COTS applications.

Call 817-274-7553 or Visit www.winsystems.com Ask about our 30-day product evaluation!

EBX

EPIC

PC/104

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

# pulse

# 32-nm CMOS begins to take shape

t the Semicon West conference in San Francisco in July, the dim outlines of 32-nm CMOS began to take shape. The process will look more familiar to design teams than many had predicted, but the process is still far from business as usual. Pacing the still-tentative discussion of 32-nm technology, Applied Materials proclaimed that 32-nm processes would continue to use planar MOSFETs. This claim represents a major change from conventional wisdom, which declares that the 32-nm process signifies the dawn of the 3-D, multigate transistor. FinFETs, trigate MOSFETs, and fully depleted SOI (siliconon-insulator) devices were all aiming to hit the mainstream at this process node.

All of these devices increase the gate's control over channel current. As channels got shorter and gate dielectrics got thinner, device physicists tried making the channel as thin as possible and surrounding it with gate electrodes to help the electric field from the gate to pinch off the channel current. The vendors thought that, with the advent of the 32-nm-process node, this approach would keep the ratio of saturation current to leakage current high enough for the transistors to be useful.

You can track the change in plans to two factors. First, the multigate devices have proved more problematic than early research suggested. The 3-D structures are difficult to fabricate reliably in the presence of production-process variations. But another problem has emerged, according to Ludo Deferm, vice president of business development at European consortium IMEC (Interuniversity Microelectronics Centre). Deferm observes that the structure of the multigate devices and fully depleted SOI transistors effectively isolate their channel regions from the underlying bulk silicon. This characteristic makes it difficult or impossible to drive contaminant atoms from the channels into underlying bulk material. The channels are so thin that the inability to purge defective atoms seriously reduces yield expectations for large dice.

Meanwhile, another factorprogress in using strain engineering to improve the saturation current of planar devicesappears to be shoving multigate devices beyond the 32-nmprocess horizon. At Semicon, both IMEC and Applied Materials reported work to increase the stress on channels in planar transistors to more than 1G pascal, doubling the channelcarrier mobility in one example.

This work yields two surprising advances. First, it shows that applying two techniques stress-reducing caps over recessed sources and drains, and over-the-top etch-stop layers to one transistor can result in more than additive increases in mobility. Second, the work at Applied Materials demonstrates improvements for both N- and P-channel devices. The company uses silicon-carbon epitaxial caps over the recessed source and drain and a tensile nitride-etch-stop layer over the top of the NMOS device, resulting in a tensile stress of 1.2G pascal. The company uses a similar structure, but with silicon-germanium epitaxy and a compressive-nitride layer, on the PMOS device. In both cases, the applied stresses are biaxial. The results are 32-nm planar P- and N-channel transistors with adequate mobility to build circuits.

However, it won't be easy for the process engineers or the circuit designers. Faran Nouri, director of Applied Materials' Applications Development Center, says that, although the company has separately fabricated N- and P-channel devices and measured their saturation currents, it has not yet fabricated them on the same wafer. Some process-integration issues will occur, she says, but the company expects no "showstoppers." Using the resulting transistors will be an issue, as well. One primary concern is the constraints that the devices will put on layout, at both the cell and the chip lev-

FROM THE VAULT "You can create efficient single-chip implementations of complex circuits. ... Semicustom-IC technology might represent the high-tech equivalent of Ben Franklin's proverbial Philosopher's Stone. ... You can now easily create fast-turnaround, inexpensive, and well-characterized customized ICs without directly designing detailed geometric masks."

Andy Rappaport, EDN, Feb 17, 1983, pg 79

els. The effect of stress on mobility depends on the orientation of the stress vector in the crystal lattice. So, the mobility of a transistor can depend on its orientation on the wafer.

More seriously, the actual stress on the channel-which the company can only simulate, not measure directly at these dimensions-highly depends on the geometry of the epitaxial caps, the etch-stop layer, and even the surrounding structures. This dependence makes the performance of each transistor on a die dependent on the geometry that surrounds it. Applied is now working with Synopsys (www. synopsys.com), and it's a good bet that other developers are also scrambling to try to figure out how to shield cell-layout engineers and circuit designers from this issue. The result could be vastly more complex placement-and-routing algorithms, the need for draconian placement and orientation rules, or both.

In addition, the enhancements to mobility of both Nand P-channel devices are changing the beta ratio, which depends on the ratio of N- to P-channel mobility. But that ratio underlies the basic design of CMOS circuits. Nouri says that the ratio is changing in today's processes, and it will continue to change. By the 32nm node, it will have changed enough to demand new circuit topologies for many common digital structures and will have uprooted current analog topologies. The future may be bleak, but it is probably happier than that for multigate transistors with their own circuit characteristics and profound issues.

-by Ron Wilson

Applied Materials, www.

amat.com.

IMEC, www.imec.be.

# The FPGA Eye Opener!

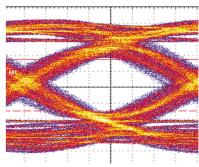

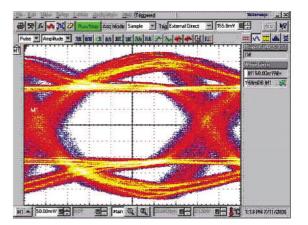

Transmit eye diagram at 6.375 Gbps. For characterization details, see www.altera.com/stratix2gx/characterization.

### The complete transceiver solution with best-in-class signal integrity.

Stratix<sup>®</sup> II GX FPGAs offer the industry's most comprehensive solution for high-speed serial applications. With significantly lower power consumption than competing devices, Stratix II GX FPGAs have up to 20 transceivers performing with exceptional noise immunity from 622 Mbps to 6.375 Gbps. Designers have immediate access to Quartus<sup>®</sup> II software support and an array of intellectual property (IP) cores, system models, development boards, and collateral—everything needed to complete a design in the shortest amount of time.

Discover Stratix II GX FPGAs today at www.altera.com.

- Up to 20 transceivers with dynamic pre-emphasis, equalization, and output voltage control

- Best-in-class signal integrity from 622 Mbps to 6.375 Gbps with exceptional channel-to-channel noise immunity

- Low power consumption (140 mW/channel at 3.125 Gbps and 240 mW/channel at 6.375 Gbps) while retaining bestin-class jitter performance

- Dedicated circuitry supporting wide range of protocol standards across multiple data rates

The Programmable Solutions Company®

www.altera.com

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights.

# pulse

## **RESEARCH UPDATE**

# Process coaxes carbon nanotubes into service as vias

esearchers at Purdue University have developed a process that grows individual carbon nanotubes vertically atop a silicon wafer. Step 1 in the process uses anodization to create an array of cylindrical pores in a thin film that features a small layer of iron between two layers of aluminum. In Step 2, the researchers flow a mixture of hydrogen and methane into the pores and use microwave radiation to break down the methane. The iron layer then acts as the catalyst for a reaction that causes carbon from the methane to selfassemble into carbon nanotubes.

The resulting vertically oriented nanotubes become, in essence, vias that could connect stacked electronic components. As with most other research involving carbon nanotubes, however, big unknowns remain. The Purdue researchers acknowledge, for example, that scientists have yet to figure out how to integrate carbon nanotubes with other types of circuitry and devices.

**Purdue University**, www. purdue.edu.

Purdue University researchers developed a process that conjures carbon nanotubes that could serve as interconnects for vertically oriented circuits.

### Your name in lights, on your body

Philips Research has demonstrated jackets featuring its Lumalive textiles, which integrate flexible arrays of LEDs into the fabric. The jackets feature  $200 \times 200$ -mm color panels and discreetly concealed battery and electronics packs that the user can, we hope, remember to disconnect and remove before washing.

The company states that the production-ready technology can scale to illuminate drapes, cushions, or even an entire sofa "to enhance the observer's mood and positively influence his behavior." We wonder how long it will be before an entrepreneurial hacker couples one of the jackets with a wireless connection and becomes a walking billboard.

Philips believes that its LED-animated textiles are where it's @.

Philips Research, www.research. philips.com.

# Magnetic material may put new spin on computing

Researchers at the Massachusetts Institute of Technology have developed a magnetic semiconductor that could bring electron "spin," which engineers already exploit in storage applications, into the realm of information processing.

The material—indium oxide with a dash of chromium—is compatible with silicon and can inject electrons of a given spin into silicon at room temperature, according to the researchers. Scientists expect that "spintronic" circuits, by encoding spin orientation in addition to current state, will deliver more computing power and versatility than traditional circuits. At the same time, because spin states are nonvolatile, spintronic circuits could drastically reduce power consumption.

The MIT group says that, although the material itself is promising, the true value of its work is more fundamental: The researchers uncovered the heretofore-elusive mechanism that governs the material's behavior.

>Massachusetts Institute of Technology, www.mit.edu.

### NANOSCALE CAVITY AMPLIFIES LED OUTPUT BY SEVEN TIMES

Precisely spaced grooves etched into a silicon cavity surrounding a semiconductor LED can make the LED as much as seven times brighter, according to researchers at NIST (National Institute of Standards and Technology).

Semiconductor LEDs typically emit only 2% of their light in the optimal direction, which is perpendicular to the diode's surface. So, NIST scientists fashioned a pattern of precisely carved and positioned grooves that causes reflections and interference that in turn shepherd more of the light in the right direction.

During several years of work honing the principle and the manufacturing technique, the scientists experimented with different arrangements of grooves. They eventually found that a structure including 10 grooves-each 240 nm wide, 150 nm deep, and 40 nm apart from each other-produces

Concentric nanoscale rings surrounding a semiconductor LED can dramatically boost the LED's light output.

the brightest output. The invention could be especially helpful in medical-imaging applications in which brightness is crucial, according to NIST.

• National Institute of Standards and Technology, www.nist.gov. 09.14.00

## "Our MCUs, Bios, and Graphics Controllers are changing

the way people interact with their cars."

Tommy Tran, Technical Sales Manager, Fujitsu Microelectronics America, Inc.

### AUTOMOTIVE EMBEDDED SEMICONDUCTOR SOLUTIONS

Fujitsu, world-renowned for quality, reliability and support, offers leading-edge embedded semiconductor solutions for the automotive industry.

### **MICROCONTROLLERS**

- 8-, 16-, 32-bit MCUs with CAN, LIN support

- Reliable and large embedded Flash memory

- 28- to 208-pin packages

### **IN-CAR NETWORK**

- FlexRay<sup>™</sup>ASSP and embedded MCU

- IDB-1394 S400 single-chip controller

### **GRAPHICS DISPLAY CONTROLLERS**

- 3D with alpha blending

- Video input with image resizing

- Wide temperature range

### **BIOMETRIC SENSORS**

- Standard CMOS technology

- Clear 500-dpi images

- Rugged, super-thin design

- World-class matching algorithm

For more information, call (800) 866-8608 or visit http://us.fujitsu.com/micro

# pulse

### **GLOBAL DESIGNER**

# Receivers target high-volume GPS and DVB-H applications

hipidea, a silicon-IP (intellectual-property) provider in Lisbon, Portugal, has expanded its IP for RF-CMOS circuit blocks with two products for handheld designs. With its IP offerings in the logic space, this mixed-signal lineup achieves a new level of antenna-tobaseband capability, according to the company. Chipidea initially created both of its new designs for specific customers and has now "generalized" them into IP platforms for the wider market. Its mobile-TV platform has three receiver paths for 176 to 245 MHz, 470 to 870 MHz, and 1.450 to 1.685 GHz, supporting DVB-H (digital-video-broadcastinghandheld), DMB (digital-multimedia-broadcasting), and ISDB-T (Integrated Services Digital Broadcasting-Terrestrial) standards.

Chipidea's designers used a direct-conversion, zero-IF architecture that needs no external SAW or IF filter and have employed a fractional-N synthesizer that can use a crystal source from the host application as a reference, further reducing the externalcomponent requirements. Operating from a 1.8 to 3.6V supply, the design uses approximately 60 mA.

The GPS (global-positioning-system)-receiver core will handle GPS and future Galileo signals in the L1 band. The receiver design's low-IF architecture needs no external IF filters. Because of the unit's low signal levels, you do need an external SAW filter, however. Power consumption is 20 mA; alternatively, if your design uses an active antenna that delivers an amplified signal, you can disable the built-in low-noise amplifier in the Chipidea IP to reduce that value to 15 mA. Chipidea is also developing an "all-systems-GPS" design that will accept ESA/ESB and E1/ L1/L2, L2 and E1/L1/E2, or E6 and E1/L1/E2 signal groupings.

Chipidea initially fabricated both chips in TSMC (Taiwan Semiconductor Manufacturing Co, www.tsmc.com) 0.18-micron CMOS, and it plans to follow the CMOS-process-migration path but only as is appropriate to the application. A DVB-H tuner is feasible in 90nm technology, according to Vice President of Engineering Carlos Leme, but the low signal levels of GPS imply that 130 nm is the minimum geometry for that task, due to factors such as the process's noise figure.

> -by Graham Prophet, EDN Europe

Chipidea, www.chipidea.com.

### New US passports contain secure identification chips

Infineon Technologies has received a multimillion-piece purchase order from the United States government to supply technology for a new electronic passport. The new passports facilitate international travel by allowing automatic identity verification, faster immigration inspections,

PASSPORT

border protection, and security. The passports include a computer chip in the back cover that securely stores the same information that is printed on the document.

"The United States is helping to set the pace for adoption of more secure travel documents around the world," says Christopher Cook, managing director of Infineon Technologies North America. "As the leading supplier of the specialized chips used for

secure personal identification, financial transactions, and access to electronic systems, our chips have successfully passed some of the most stringent security tests in the world. We are happy to be chosen to supply the electronics for the large-scale roll-out of the US electronic passport."

The electronic passport has mul-

New US passports will integrate chips from Infineon Technologies.

tiple layers of security to protect the privacy of holders. These layers include basic-access control, which requires the border-control inspector to pass the document over a scanner that reads coded information and then authorizes the electronic reader to access the data stored on the chip. The actual data transmission occurs over a distance of about 4 in. (10 cm).

In addition to shielding and basic-access control, the chip has more than 50 security mechanisms, including sophisticated computing methods for encrypting data, to help ensure that personal data remains private. Security mechanisms also include active protective shields on the surface of the chip and sensors that help prevent unauthorized people from being able to read the contents of the chip.

-by Vinod Kataria, EDN Asia Infineon Technologies, www.infineon.com. 09.14.06

United States of America

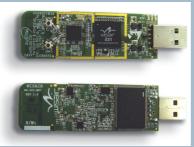

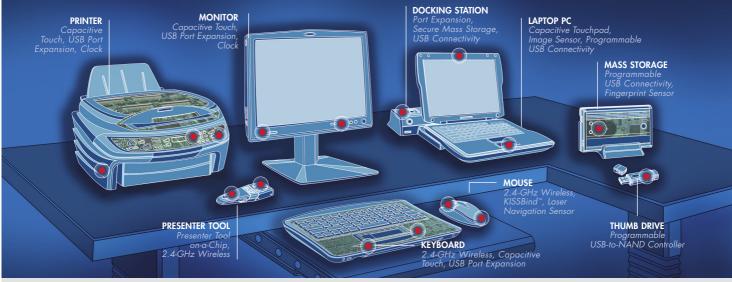

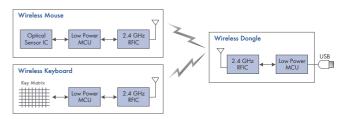

### Wireless System Challenges continued from page 1

To avoid the need to develop with two (or more) different sets of development tools, select a single family of MCUs, including both USB and low power devices, so that firmware development across the system uses a single tool chain. If possible, it is also advantageous to select the MCU family and the RFIC from the same vendor, because the protocol firmware will be available for these MCUs eliminating the need to port the firmware from another MCU. However, just as protocol is a key criterion for selecting the RFIC, so the features and quality of the development tools are an essential part of selecting the MCU. An Integrated Development Environment (IDE), In-Circuit Emulator (ICE) and source-level debugging (if developing in "C") are essential for fast and effective firmware development - even if the code size will be small. Most firmware engineers have written custom RS232 debugging output firmware, but with the widespread availability of high quality IDEs and ICEs the old "roll your own" approach to debugging is no longer competitive.

### The Benefits of In-System Reprogrammability

Selection of a Flash-based rather than One-Time-Programmable (OTP) or Mask ROM MCU will help you throughout the development process by enabling In-System Reprogrammability (ISR). Making a firmware change during development and testing no longer means unscrewing the enclosure, removing the PCB, and then desoldering the MCU. With a Flash MCU and a well-positioned ISR header (for example inside the battery compartment) uploading code changes is easy – you can even upgrade prototypes in the hands of beta testers by simply emailing them a new hex file, rather than having to send out a costly series of new prototypes. Some USB MCU vendors even support reprogramming over USB – eliminating even the need for a special programmer during development of the RF dongle.

Another consideration is the level of support you can expect from your chosen RFIC and MCU vendors; do they have a portfolio of application notes and reference designs to get you started? Is there a knowledgeable Field Applications Engineer (FAE) in your area? How much do the MCU vendor FAEs know about RF? Selecting a single vendor for both RFIC and MCUs with a worldwide support network will ensure your success if you run into problems.

### Navigating Manufacturing Test

One important area often overlooked by first-time developers of 2.4. GHz products is manufacturing test, along with the related aspects of regulatory compliance. A single poor solder joint on one of the components between the RFIC and the antenna, or even a simple problem with a decoupling capacitor, could cause a change in the RF spectrum of your product, causing it to violate regulatory compliance standards even though it still passed a simple, functional final manufacturing test. Some form of radiated testing during manufacturing is essential for preventing the shipment of non-compliant devices that result from minor manufacturing defects — this will require the development of special test firmware. The conventional approach to radiated testing is to test in a screened room with an operator checking the transmitted spectrum using a spectrum analyzer connected to an antenna. However, this approach is costly, both in labor and the cost of the screened room facilities. An equally effective, but dramatically lower cost solution is to use a small screened test box lined with RFabsorbent foam and a Bit Error Rate (BER) tester. By performing BER testing close to the limit of sensitivity it is possible to detect any manufacturing defects in the RF subsystem. Some RFIC manufacturers provide a complete reference design for this approach, eliminating the need for you to begin from scratch; all you need to do is integrate the provided test firmware into your code.

One option is to include this test firmware in the main code, with entry to the test mode being triggered by a special button press sequence during and immediately after power-on. However, if you are using an ISR-capable Flash MCU, the burden of this firmware on the limited available memory can be eliminated by programming the product with the special test firmware image during manufacturing, and then replacing it with the final product code after RF test.

As we have seen, careful consideration of the system-level challenges when selecting key components can ease the design challenges facing the designer of wireless input devices. However, these lessons go far beyond this specific application – selecting programmable solutions with comprehensive development tools and support is a key first step to success for any new product development.

### Cypress Solutions: What's In it for You?

Whether you're upgrading your user interface with capacitive sensing technology, or adding state-of-the-art biometric security to a thumb drive, Cypress PC Peripheral solutions offer the following benefits:

**Programmability:** Cypress was an early innovator of In-System Reprogrammable<sup>™</sup> (ISR<sup>™</sup>) products, enabling you to make design changes all the way through the development and testing phases.

**Integration:** Cypress offers highly integrated devices for the PC peripheral market, including our award-winning PRoC<sup>™</sup> solution that combines a programmable microcontroller with our 2.4-GHz WirelessUSB<sup>™</sup> radio-on-a-chip.

Whole Product Support: Cypress support goes beyond datasheets and application notes. We provide a broad array of development kits, reference designs, test kits and demo boards that make your job easier and reduce design time and cost.

To register for a free net seminar: "Cypress HID Solutions – Savings from Concept to Production" – visit www.cypress.com/shortlink

Cypress, the Cypress logo and PSoC are registered trademarks and erCoRe, In-System Reprogrammable, ISR, KISSBind, PRoC, Programmable Systemon-Chip, and WirelessUSB are trademarks of Cypress Semiconductor Corporation. All other trademarks are properties of their respective owners. @2006 Cypress Semiconductor Corporation. All rights reserved.

### For additional resources, visit us at **www.cypress.com/peripherals**

# Cypress PC Peripheral Solutions

**Cypress's flexible system solutions** get you to market faster with the silicon, software and technical support to assist you every step of the way. For a complete selection of application notes, reference designs, boards, kits and models – or for direct links to solutions in the graphic above – check out our PC Peripheral Solutions center at www.cypress.com/peripherals.

## Addressing the System-Level Challenges of Wireless Input Devices

by David Wright, Member of the Technical Staff, Cypress Semiconductor Corp.

The article below, one in a series of design solutions pieces for EDN readers, explores some of the challenges facing designers of wireless PC Peripherals. For access to Cypress's library of extensive staffwritten contributed articles, visit us at **www.cypress.com/techlibrary.**

The popularity of wireless input devices (mice, keyboards, gamepads, etc.) continues to grow, but designing with these products generally involves a significant increase in complexity compared with their "wired" predecessors (usually USB).

Which RF technology will you choose? How to sort out options related to the MCU and its development tools. Will you opt for programmable or fixed-function devices – for standard ICs or proprietary solutions? Finally, if you are designing with 2.4-GHz wireless technology, how will you handle the manufacturing test phase where a single poor solder joint can throw your system out of whack and bring on a regulatory violation?

Let's take a look at some of the more common pitfalls in the design process and some basic ways to avoid them.

### **Picking the Radio**